## **Description**

SE8406 is a step-down DC/DC regulator with an internal switch, featuring SKIP control mode, which combines low quiescent current with high switching frequency to achieve high-efficiency regulation over a wide range of load currents. SKIP mode uses a short "burst" cycle to switch the inductor current through the internal power MOSFET, followed by a sleep cycle in which the power switch is turned off and the load current is provided by the output capacitor. At light loads, burst cycles are a small fraction of the total cycle time, minimizing average supply current and greatly improving efficiency at light loads.

SE8406 has a wide input voltage range of 4V-60V, thus minimizing the need for external surge suppression components. Making it the best choice for wide input power range industrial and high cell count battery pack applications. SE8406 is ideal for use in the 48V automotive power bus range.

SE8406 features low-value  $100m\Omega$  high-side and  $80m\Omega$  low-side MOSFET that provide at least 3A output current capability with excellent load and line transient response.

Additional features include: soft-start, thermal shutdown, UVLO undervoltage lockout, gate driver undervoltage lockout, maximum duty cycle limit timer, and current limit shutdown timer. It also integrates output short-circuit protection, providing HICCUP mode when the FB voltage is low to avoid overheating during short-circuit.

# **Features**

- Input voltage range: 4V-60V

- Output voltage range: 1V-VIN

- Integrated upper and lower power MOSFET output current: 3.5A

- Up to 99% efficiency (in the case of input and output low dropout)

- 20μA Quiescent current in regulation

- Adjustable frequency range: 200KHz~2.5MHz

- Automatic switching of CCM/DCM/PFM mode

- Adjustable soft-start time and Output voltage tracking capability

- Automatically switched bypass linear power supply, improve high-voltage light-load efficiency

- Provides ultra-low input and output dropout voltage close to 100% duty cycle

- Internal Compensation

- Power-good flag

- Dynamic Frequency Stretch Technology

- Support large capacitive load start-up

- Protection function: UVLO/OCP/SCP/OTP/OVP

- Operating temperature range: -40°C to +125°C

- All pins have ±2000V (HBM) ESD protection

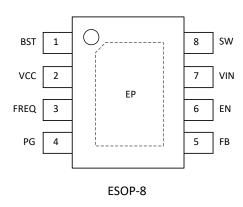

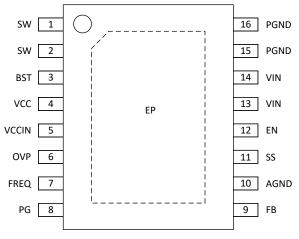

- ESOP-8 and ETSSOP-16 Exposed Pad Package

## **Applications**

- Automotive Systems and Industry Systems

- Distributed Power Systems

- Battery Powered Systems

- GPS tracker, Charger in vehicle

- Motor Drives, Telecom

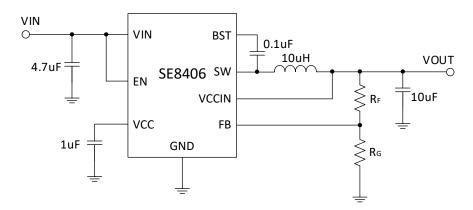

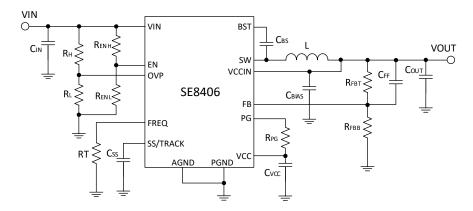

## **Typical Application Circuit**

## **Pin Configuration**

ETSSOP-16

# **Functional Pin Description**

| PIN      |       | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|----------|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ETSSOP16 | ESOP8 | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 1,2      | 8     | SW       | Internal power switch node. Externally connected to power inductor and CBST capacitor.                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 3        | 1     | BST      | Bootstrap drive power supply. High quality 100nF ceramic capacitors need to be connected between the BST and SW to bias the internal high voltage side gate driver.                                                                                                                                                                                                                          |  |  |  |  |

| 4        | 2     | VCC      | A power supply to supply power to the internal control circuit. A 1uF~4.7uF ceramic decoupling capacitor must be connected between VCC and PGND, as close as possible to the chip pin. VCC is powered by VIN or VCCIN.                                                                                                                                                                       |  |  |  |  |

| 5        | /     | VCCIN    | VCC is powered by VIN by default, If VCCIN conditions are suitable, it can be adaptively switched to VCCIN power supply to reduce the loss caused by VIN power supply. If not, the VCCIN can be grounded.                                                                                                                                                                                    |  |  |  |  |

| 6        | /     | OVP      | Overvoltage protection pin, connected to the input pin and ground divider resistance.                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 7        | 3     | FREQ     | Step-down transformer working frequency setting pin, a suitable resistance is connected between FREQ and PGND, and the switching frequency can be adjusted from 200KHz to 2MHz.                                                                                                                                                                                                              |  |  |  |  |

| 8        | 4     | PG       | Open-drain indicates that the output voltage of the step-down transformer is normal. When the output is normal, PG stops pulling down.                                                                                                                                                                                                                                                       |  |  |  |  |

| 9        | 5     | FB       | Output voltage feedback pin. The output voltage can be adjusted by configuring the partial voltage ratio between VOUT and PGND.                                                                                                                                                                                                                                                              |  |  |  |  |

| 10       | EP    | GND      | Chip simulates ground pins.                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 11       | /     | SS/TRACK | Soft start and voltage tracking pins. The voltage of this pin is used to set the reference source of the control loop. When internal soft start is selected, the pin should be suspended; When selecting soft start with external control, connect appropriate capacitor between SS/TRACK and PGND; When choosing to use voltage tracing, connect SS/TRK to the voltage source to be traced. |  |  |  |  |

| 12       | 6     | EN       | Voltage regulator output enable pin, set high enable output. The undervoltage protection of VIN can be set by configuring the external resistor divider.                                                                                                                                                                                                                                     |  |  |  |  |

| 13,14    | 7     | VIN      | Voltage regulator power input. Use a ceramic capacitor of $2.2\mu F$ or larger as close as possible to the bypass VIN to PGND.                                                                                                                                                                                                                                                               |  |  |  |  |

| 15,16    | EP    | PGND     | Power ground pins, which are connected to VIN with one or more decoupled ceramic capacitors, as close to the pins as possible.                                                                                                                                                                                                                                                               |  |  |  |  |

| EP       | EP    | GND      | Metal heat sink, connected to PGND.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

# **Ordering Information**

| Product model | Packaging form | Smallest packaging | Logo    | Output current |

|---------------|----------------|--------------------|---------|----------------|

| SE8406E       | ESOP8          | 4000PCS            | SE8406E | 3.5A           |

| SE8406T       | ESSOP-16       | 4000PCS            | SE8406T | 3.5A           |

# **Absolute Maximum Ratings**(†)

| Parameter                                   | Range          |

|---------------------------------------------|----------------|

| Pin to GND Voltage (VIN,SW,EN)              | -0.3V~65V      |

| Pin to GND Voltage (BST)                    | -0.3V~SW+6V    |

| Pin to GND Voltage (FB, FREQ, SS, OVP, VCC) | -0.3~6V        |

| Pin to GND Voltage (VCCIN, PG)              | -0.3~6V        |

| Storage temperature                         | -65°C to 150°C |

| Operating temperature                       | -40°C to 125°C |

| ESD Value (HBM)                             | ±2KV           |

| ESD Value (CDM)                             | ±1KV           |

**†**NOTE: If the operating conditions of the device exceed the absolute maximum, the device may be permanently damaged. This is only a limit parameter and it is not recommended that the device operate at or above the limit value. The reliability of devices may be affected by long time operation in limiting conditions.

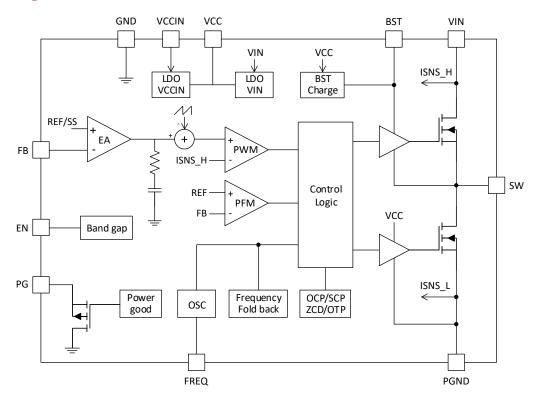

## **Block Diagram**

## **Electrical Characteristics**

Limits apply to operating junction temperatures (T<sub>J</sub>) ranging from -40°C to +125°C unless otherwise specified. Minimum and maximum limits are specified by test, design or statistical correlation. Typical values represent the most likely parameter specifications when T<sub>J</sub>=25°C, for reference only. All voltages are relative to GND.

| PARAMETER            |                                          | TEST CONDITIONS                                                                     | MIN  | TYP   | MAX  | UNIT |

|----------------------|------------------------------------------|-------------------------------------------------------------------------------------|------|-------|------|------|

| Input Charact        | eristics                                 |                                                                                     |      |       | _    |      |

| V <sub>IN</sub>      | Operating Input Voltage<br>Range         |                                                                                     | 4    |       | 60   | V    |

| V <sub>IN_GD</sub>   | VIN undervoltage leek                    | Rising                                                                              |      | 4     |      | V    |

|                      | VIN undervoltage lock                    | Falling                                                                             |      | 3.6   |      | V    |

| V                    | VCCIN payor good                         | Rising                                                                              |      | 3.9   |      | V    |

| V <sub>CCIN_GD</sub> | VCCIN power good                         | Falling                                                                             |      | 3.5   |      | V    |

| I <sub>Q_VIN</sub>   | VIN Operating quiescent current          | V <sub>IN</sub> =EN=24V, V <sub>FB</sub> =1.2V<br>V <sub>CCIN</sub> = 5V, No switch |      | 10    | 12   | uA   |

| I <sub>Q_VCCIN</sub> | VCCIN Operating quiescent current        | V <sub>IN</sub> =EN=24V, V <sub>FB</sub> =1.2V<br>V <sub>CCIN</sub> = 5V, No switch |      | 50    | 60   | uA   |

| IQ                   | VIN Equivalent quiescent current         | V <sub>IN</sub> =EN=24V<br>V <sub>CCIN</sub> = V <sub>OUT</sub> =5V, No switch      |      | 25    |      | uA   |

| I <sub>SD</sub>      | Shutdown quiescent current               | EN=0, V <sub>IN</sub> =60V                                                          |      |       | 2    | uA   |

| VCC Characte         | ristics                                  |                                                                                     |      |       |      |      |

| V <sub>CC</sub>      | VCC output voltage                       | VIN=24V                                                                             | 4.8  | 5.0   | 5.2  | V    |

| V <sub>CC_GD</sub>   |                                          | Rising                                                                              |      | 3.5   |      | V    |

|                      | VCC undervoltage protection              | Falling                                                                             |      | 3.2   |      | V    |

| I <sub>SC_VCC1</sub> | VCC short circuit current (VIN supply)   | VIN=24V, VCCIN=0V                                                                   |      | 20    |      | mA   |

| I <sub>SC_VCC2</sub> | VCC short circuit current (VCCIN supply) | VIN=VCCIN=24V,                                                                      |      | 20    |      | mA   |

| FB PIN               |                                          | '                                                                                   | '    |       | '    |      |

| V <sub>FB_acc</sub>  | FB feedback voltage                      |                                                                                     | 0.99 | 1.0   | 1.01 | V    |

| V <sub>FB_GD</sub>   | FB good threshold value                  |                                                                                     | 0.83 | 0.85  | 0.87 | V    |

| V <sub>FB_OV</sub>   | FB Over voltage threshold                |                                                                                     | 1.12 | 1.15  | 1.18 | V    |

| V <sub>FB_skip</sub> | FB Jump period threshold                 |                                                                                     |      | 1.003 |      | V    |

| I <sub>FB_leak</sub> | FB The leakage current                   |                                                                                     |      |       | 30   | nA   |

| PWM Related          | <u> </u>                                 |                                                                                     | - 1  |       | '    |      |

| R <sub>DS_HS</sub>   | High-side MOSFET ON-<br>resistance       | TJ= 25°C                                                                            |      | 100   | 160  | mΩ   |

| R <sub>DS_LS</sub>   | Low-side MOSFET ON-<br>resistance        | TJ= 25°C                                                                            |      | 80    | 130  | mΩ   |

| I <sub>Peak_HS</sub> | HS Current limit                         |                                                                                     | 3.8  | 4.2   | 4.8  | А    |

| I <sub>Peak_LS</sub> | LS Current limit                         |                                                                                     | 4    | 4.5   | 5    | Α    |

| I <sub>ZCD</sub>     | LS Current zero                          |                                                                                     |      | 50    |      | mA   |

| I <sub>SW.LKG</sub>  | SW Leakage current                       |                                                                                     |      |       | 1    | uA   |

| F <sub>SW</sub>      | Switching frequency                      | PWM Operation                                                                       | 0.9  | 1.0   | 1.1  | MHz  |

|                          | accuracy                                                                        | $R_{FREQ} = 62k\Omega$    |      |      |      |      |

|--------------------------|---------------------------------------------------------------------------------|---------------------------|------|------|------|------|

| F <sub>SW_range</sub>    | Switching frequency range                                                       | with 1% R <sub>FREQ</sub> | 0.2  |      | 2.0  | MHz  |

| D <sub>MAX</sub>         | Maximum duty cycle                                                              | VIN=12V, VOUT=11.9V       | 99   |      |      | %    |

| Tss                      | Soft start time                                                                 |                           | 200  | 300  | 400  | us   |

| T <sub>HSON.MIN</sub>    | HS Minimum turn-on time                                                         |                           |      | 80   | 110  | ns   |

| T <sub>HSON.MAX</sub>    | HS Maximum conduction time                                                      |                           |      | 8.0  |      | us   |

| T <sub>LSON.MIN</sub>    | LS Minimum turn-on time                                                         |                           |      | 60   | 100  | ns   |

| t <sub>SS</sub>          | Soft start time                                                                 |                           |      | 400  |      | us   |

| T <sub>SCP_HOLD</sub>    | Trigger time of short circuit protection                                        |                           |      | 3    |      | ms   |

| T <sub>SCP_HICCUP</sub>  | Short circuit protection hiccup waiting time                                    |                           |      | 6    |      | ms   |

| EN PIN                   |                                                                                 |                           |      |      |      |      |

| V <sub>EN_H</sub>        | EN High logic threshold                                                         |                           | 1.1  |      |      | V    |

| V <sub>EN_L</sub>        | EN LOW logic threshold                                                          |                           |      |      | 0.5  | V    |

| V <sub>EN_UV_R</sub>     | EN Undervoltage protection rising edge                                          |                           | 1.19 | 1.2  | 1.21 | V    |

| V <sub>EN_UV_F</sub>     | EN Undervoltage protection falling edge                                         |                           | 1.14 | 1.15 | 1.16 | V    |

| I <sub>LKG-EN</sub>      | EN Input current                                                                | EN < 60V                  |      |      | 1    | uA   |

| Thermal prote            | ction characteristic                                                            |                           |      |      |      |      |

| T <sub>OTP-R</sub>       | Over temperature protection                                                     | T <sub>J</sub> Rising     |      | 160  |      | °C   |

| Тотр-ғ                   | The overtemperature protection is removed                                       | T <sub>J</sub> Falling    |      | 145  |      | °C   |

| Thermal resista          | ance coefficient                                                                |                           | •    |      |      | •    |

| $\theta_{JA}$            | The thermal resistance coefficient from the silicon core to the surrounding air | 0 LFPM Air Flow           |      | TBD  |      | °C/W |

| $\theta_{JB}$            | Thermal resistance coefficient between silicon core and PCB surface             |                           |      | TBD  |      | °C/W |

| $\theta_{	extsf{JCtop}}$ | Thermal resistance coefficient of silicon core to upper surface of package      |                           |      | TBD  |      | °C/W |

| $\Psi_{JB}$              | Thermal resistance coefficient between silicon core and PCB surface             |                           |      | TBD  |      | °C/W |

## **Application information**

#### Overview

SE8406 is a high efficiency, high power density synchronous buck converter. The chip has an input voltage range of 4V to 60V, and is internally integrated with upper and lower power Mos tubes, which can output up to 3A load current. And can provide a stable output voltage from 1V to VIN.

SE8406 has SKIP control mode, which combines low static current with high switching frequency to achieve high efficiency over a wide range of load current. Fixed frequency peak current control mode with integrated internal compensation is adopted to shorten design time and require fewer external devices. SE8406 adjusts the switching frequency from 200kHz to 2MHz through an external resistor. The wide switching frequency range allows the chip to be optimized for small volume requirements at higher frequencies or efficient power supplies at lower frequencies. In addition, SE8406 can operate at close to 100% of the maximum duty cycle to achieve the best possible input-output differential pressure. SE8406 integrates a bypass LDO linear power supply, which can be connected to an external low-voltage power supply to generate VCC, further improving the chip's light-load efficiency under high voltage input conditions. The chip provides the automatic detection and switching circuit of bypass LDO. When the bypass LDO is directly connected to VOUT and the VOUT rises above the switching threshold, the internal LDO input power can be seamlessly switched from VIN to VOUT.

SE8406 also offers a variety of other features, including an external resistor to adjust the output voltage, a choice of built-in soft start or external adjustable soft start, an output voltage follow function, and a good sign of power supply. Protection features include periodic peak and trough current limiting, output short-circuit protection in Hiccup mode, input overvoltage protection for hot swap applications, thermal turn-off and self-recovery, and precise input undervoltage protection.

#### EN enable

EN pin voltage control SE8406 internal VCC LDO linear power supply and synchronous buck converter output VOUT on and off. When  $V_{EN}$  is lower than  $V_{EN\_L}$ , the chip enters the shutdown mode to maintain the low-power standby state. At this time, the maximum input current of the chip will not exceed 2uA.

The EN pin has a precise threshold,  $V_{EN\_UV}$ , to control the startup and shutdown of SE8406. When the EN voltage rises above this threshold, the chip output is allowed. In practical applications, two resistors are connected in series between VIN and PGND pins, and the center point of the two resistors is connected to EN pins, and the adjustable input UVLO protection is realized through the two resistors. The UVLO value can be determined by the following formula:

$$V_{IN\_RISING} = (1 + \frac{R_{ENH}}{R_{ENL}}) \times V_{EN\_UV\_R}$$

#### Internal LDO linear power supply, VCC and VCCIN pin

SE8406 integrates an LDO linear power supply to provide VCC power for the control circuit and MOSFET drive. The VCC has a nominal voltage of 5V and the pin must be connected to PGND as close to the pin as possible via a ceramic decoupling capacitor of 1uF-4.7uF. The internal LDO has two inputs: one from VIN and one from VCCIN pins. When THE VCCIN voltage is higher than the switchover threshold, the VCCIN input supplies power to THE LDO. The power loss of LDO can be calculated by the following formula:

$$ILDO \times (VIN_{LDO} - VOUT_{LDO})$$

The greater the pressure difference between the input and output voltages of LDO, the greater the loss. The VCCIN input is designed to reduce the voltage difference between the input and output voltage of the LDO to reduce power losses and improve efficiency, especially under light load. When VCCIN is not used as LDO linear power input, connect VCCIN directly to PGND.

#### The output voltage VOUT and FB pin

SE8406 voltage regulation loop will adjust the FB voltage to be the same as the internal reference voltage, and the output voltage can be adjusted by changing the resistance ratio of the upper divider  $R_{FBT}$  to the lower divider  $R_{FBB}$ . Connect the resistance divider between the output node and ground, with the middle point connected to the FB pin. The steady-state voltage of  $V_{FB}$  is usually 1V.  $R_{FBB}$  can be calculated by the following formula:

$$R_{FBB} = (\frac{V_{FB}}{V_{OUT} - V_{FB}}) \times R_{FBT}$$

The choice of  $R_{FBB}$  depends on the application environment. A large divider resistance can reduce the current flowing over the overvoltage network, but a large resistance makes the feedback loop more susceptible to noise. It is recommended that the  $R_{FBB}$  be set to a maximum of  $1M\Omega$ . Large precision error and temperature coefficient affect the control precision of output voltage. It is recommended to use a resistor with precision error less than 1% and temperature coefficient less than 100ppm.

The feedback loop should be kept away from the interference of PCB noise. Refer to the PCB layout for reference.

#### Internal compensation and CFF

SE8406 internal compensation makes the chip stable over the entire operating frequency and output voltage range. Depending on the output voltage, the phase margin of the compensation loop may be low. It is recommended that an external feedforward capacitor,  $C_{FF}$ , be connected in parallel with an upper divider,  $R_{FBT}$ , for optimal transient performance. See figure 5 for details.

The feedforward capacitor  $C_{FF}$  is in parallel with  $R_{FBT}$ , and zero is added before the crossing frequency of the control loop to improve the phase margin. The zero frequency can be obtained by the following formula:

$$f_{Z-CFF} = \frac{1}{2\pi \times R_{FBT} \times C_{FF}}$$

At the same time, poles are introduced, and the frequency of poles is:

$$f_{P-CFF} = \frac{1}{2\pi \times C_{FF} \times (R_{FBT}//R_{FBB})}$$

Different output capacitor combination designs require different  $C_{FF}$ . Different types of capacitors have different equivalent series resistance (ESR). Ceramic capacitors have minimum ESR and highest  $C_{FF}$  requirements. Electrolytic capacitors have larger ESR, and the zero frequency produced by ESR will be low enough to increase the phase prior to frequency crossing. Designs using large ESR capacitors at the output may not require any  $C_{FF}$ , and the zero ESR frequency is as follows:

$$f_{Z-ES} = \frac{1}{2\pi \times ESR \times C_{OUT}}$$

## Power supply normal mark (Power Good)

PG pin is connected to the drain of an internal MOSFET. The PG pin needs to be pulled up to the VCC or external power supply by an external resistor. The voltage detected by the PG pin shall not exceed 12V. A resistance divider may be used to divide voltage from higher voltages. Pull-up resistors typically range from  $10k\Omega$  to  $100k\Omega$ . When the FB voltage is within the normal range of the power supply, the PG internal MOSFET is off and the PG pin is in a high level state. Conversely, when the FB voltage exceeds the normal output tolerance range, usually+15% above the internal reference voltage or -15% below, the PG pin internal MOSFET is turned on and the PG pin voltage is pulled down to indicate a power supply failure. To prevent burrs from affecting THE PG function, there is a 320us delay for both the PG pin pull up and pull down.

SE8406 Nebula Semiconductor Technology Co., LTD

## Soft start and output voltage tracking function

SE8406 allows internal soft start or external soft start. The SS/TRK pins should be suspended when internal soft start is selected, and SE8406 uses internal soft start control to output oblique waves, usually starting to a stable output voltage around 300us. In applications with large output capacitors, high output voltages, or other special requirements, a C<sub>SS</sub> capacitor can be connected to this pin to AGND to extend soft start time. Extending the soft start time further reduces the current required to charge the output capacitor and provide the output load. SE8406 has an internal 2.6uA constant current source to charge the C<sub>SS</sub> capacitor, so the external soft start time can be calculated by the following formula:

$$t_{ss} = C_{SS} \times \frac{V_{REF}}{I_{SS\_CHARGE}}$$

SE8406 can use this pin to follow the output voltage to the external power supply. When this function is required, connect the SS/TRK pin to the voltage source to be tracked, and the  $V_{FB}$  will follow the voltage  $V_{SS}$  applied to the SS/TRK pin. When the  $V_{SS}$  is greater than 1V, the  $V_{FB}$  is controlled at an internal reference voltage of 1V.

SE8406 can be started with pre-biased output. When the inductance current reaches zero, the lower tube is turned off to avoid negative current conduction. This mode of operation is also called diode simulation mode. With a pre-biased output voltage, SE8406 waits until the soft-start ramp allows adjustment above the pre-biased voltage, and then follows the soft-start ramp to the adjustment level.

## Switching frequency and FREQ pin

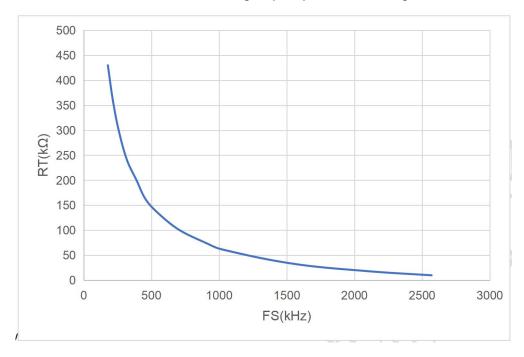

The switching frequency of SE8406 can be determined by the external resistor  $R_T$  connected between FREQ pins and AGND, which ranges from 200kHz to 2.5MHz.  $R_T$  can be calculated by the following formula:

$$R_T(k\Omega) = \frac{81053}{Fs(kHz)} - 21$$

The relation curve between R<sub>T</sub> resistance and switching frequency is shown in the figure below

For common switching frequencies, R<sub>T</sub> Settings can be referred to the following table

| $R_T(k\Omega)$ | Fs(kHz) |

|----------------|---------|

| 10             | 2500    |

| 18             | 2100    |

| 33             | 1500    |

| 62             | 1000    |

| 160            | 500     |

| 200            | 400     |

| 470            | 200     |

### BST and SW pin

SE8406 requires a small ceramic capacitor between the BST and SW pins to provide the gate drive voltage for the high-side MOSFET. When the high side MOSFET is off and the low side MOSFET is on, the C<sub>BST</sub> capacitor charges. The ceramic capacitor shall have a maximum of 0.47uF and be connected between BST and SW for proper operation. Class X7R or X5R dielectric ceramic capacitors are recommended because of their stable temperature and voltage characteristics. Ceramic capacitors shall be rated at 16V or higher.

### Low Drop-Out mode

When the input voltage approaches the set output voltage, SE8406 enters the Low drop-out mode. At this point, the switching time of a single period of the high-side power tube is allowed to exceed the set switching period, and the switching time is automatically adjusted with the input voltage to maintain the control of the output voltage. When the input voltage is lower than the set output voltage, the maximum conduction time of the high-side power tube is limited to T<sub>HSON.MAX</sub>. At this time, the low-side power tube will temporarily conduct T<sub>LSON.MIN</sub> to realize charging of C<sub>BST</sub>. Ensure that the C<sub>BST</sub> has enough voltage to maintain the normal operation of the high side power tube drive circuit.

#### Overcurrent protection and short circuit protection

SE8406 prevents overcurrent conditions by periodic limits on peak and trough values of inductive current. If the overcurrent condition persists, the hiccup mode will be triggered to prevent the chip from overheating.

High - side MOSFET overcurrent protection is achieved by the characteristics of peak current control mode. The output of the error amplifier after subtracting the oblique wave compensation for each switching period is compared with the current of the high side power tube sampled, please refer to the functional block diagram for details. Therefore, the peak current of the high-side power tube is restricted by the maximum output of the error amplifier, so as to achieve the ability of periodic peak current limitation.

SE8406 detects the current of the low-side power tube and compares it with the valley bottom current limiting threshold during low-side MOSFET conduction. When the current of the low-side power tube is higher than the bottom current limiting threshold, the high-side power tube is not allowed to run until the low-side power tube is lower than the bottom current limiting threshold.

SE8406 enters Hiccup mode when the high-side power tube current triggers the error amplifier limit and the power supply normal indicator is pulled down. At this point, the chip will shut down the output and hold for 5ms, then the chip will try to restart. If the overcurrent or short circuit fault state still exists, the hiccup will be repeated until the fault state is over. Hiccup mode reduces power consumption under severe overcurrent or short circuit conditions and prevents overheating from damaging the chip.

SE8406

Nebula Semiconductor Technology Co., LTD

### Over temperature protection

The thermal overload protection circuit limits the junction temperature to below 160°C (typical value). Under extreme conditions (high ambient temperature and/or high power consumption), when junction temperature begins to rise above 160°C, overtemperature protection is activated and the system will forcibly shut down the regulator output.

When the junction temperature drops below 145°C, the OTP state will be unlocked, the regulator output will be turned on again, and the output current will return to normal operating value. Thermal overload protection is designed to protect the device from transient accidental overload conditions.

The device has a guaranteed operating junction temperature range of -40°C to 125°C. High junction temperature will reduce the working life; The device life is shortened when the junction temperature is 125°C for a long time. Please note that the maximum ambient temperature consistent with these specifications depends on the specific operating conditions as well as the PCB layout, package thermal rating, and other environmental factors. Junction temperature (T<sub>J</sub>, unit: °C) is calculated according to the ambient temperature (T<sub>A</sub>, unit: °C) and power consumption (P<sub>D</sub>, unit: W). The calculation formula is as follows:

$$T_I = T_A + (P_D \times \theta_{IA})$$

$\theta_{IA}$  (unit: °C/W) is the thermal resistance of packaging.

#### Input undervoltage locked

When VIN voltage falls below the UVLO drop threshold, UVLO protection is triggered, shutting down the regulator output. The rise threshold of the UVLO is about 4V, and when VIN reaches the voltage above this, the controller will enter the soft start process after removing the UVLO.

#### SKIP pulse mode

SE8406 built-in pulse hopping circuit; In light load, the circuit is closed; Switch only when necessary to keep the output voltage within the specified range. This reduces switching losses and allows the driver to remain efficient under light loads.

In pulse-jump mode, when the output voltage falls below a specified value, SE8406 enters PWM mode and stays for several oscillator cycles to bring the output voltage up to a specified range. During the waiting time between bursts of pulses, the power switch is switched off and the output capacitor provides all the load current. The output voltage ripple in this mode is larger than that in PWM mode because the output voltage will drop and recover irregularly.

SE8406 10 / 16

Nebula Semiconductor Technology Co., LTD www.nblsemi.com

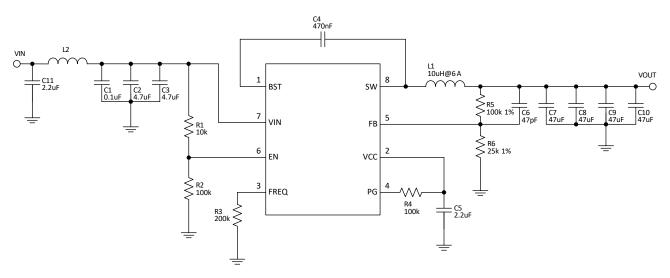

## Fully functional application circuit diagram

ETSSOP-16 Typical application

#### NOTE:

- 1) It is recommended to use 10uF X7R or X5R ceramic capacitor for input capacitor, and place it as close as possible to power input pins 4 and 5

- 2) For C<sub>BST</sub>, please select a ceramic capacitor with a voltage withstand of more than 16V and place it as close to pins 1 and 6 as possible

**ESOP8** Typical application

## Table of external devices for typical applications

| $R_{FREQ}(k\Omega)$ | V <sub>OUT</sub> (V) | V <sub>IN_Range</sub> (V) | C <sub>OUT</sub> (uF) <sup>(3)</sup> | L(uH) <sup>(2)</sup> | $R_{FBT}(k\Omega)^{(5)}$ | $R_{FBB}(k\Omega)^{(5)}$ | C <sub>ff</sub> (pF) <sup>(6)</sup> |

|---------------------|----------------------|---------------------------|--------------------------------------|----------------------|--------------------------|--------------------------|-------------------------------------|

| Fs=2MHz             |                      |                           |                                      |                      | •                        |                          |                                     |

|                     | 3.3                  | 4-15 <sup>(1)</sup>       | 47                                   | 2.2                  | 100                      | 43.2                     | 47                                  |

| 18.7kΩ              | 5                    | 5-24 <sup>(1)</sup>       | 47                                   | 2.2                  | 100                      | 24.9                     | 47                                  |

| 18.7KΩ              | 12                   | 12-60 <sup>(4)</sup>      | 22                                   | 8.2                  | 100                      | 9.09                     | NA                                  |

|                     | 24                   | 24-60 <sup>(4)</sup>      | 22                                   | 15                   | 100                      | 4.32                     | NA                                  |

| Fs=1MHz             |                      |                           |                                      |                      |                          |                          |                                     |

|                     | 1                    | 4-9(1)                    | 100                                  | 2.2                  | Short                    | Open                     | Short                               |

|                     | 3.3                  | 4-30 <sup>(1)</sup>       | 100                                  | 6.8                  | 100                      | 43.2                     | 47                                  |

| 64.9kΩ              | 5                    | 5-60                      | 100                                  | 8.2                  | 100                      | 24.9                     | 47                                  |

|                     | 12                   | 12-60                     | 22                                   | 18                   | 100                      | 9.09                     | NA                                  |

|                     | 24                   | 24-60                     | 22                                   | 27                   | 100                      | 4.32                     | NA                                  |

| Fs=400kHz           |                      |                           |                                      |                      |                          |                          |                                     |

|                     | 1                    | 4-21 <sup>(1)</sup>       | 200                                  | 4.7                  | Short                    | Open                     | Short                               |

|                     | 3.3                  | 4-60                      | 100                                  | 10                   | 100                      | 43.2                     | 47                                  |

| 200kΩ               | 5                    | 5-60                      | 100                                  | 10                   | 100                      | 24.9                     | 47                                  |

|                     | 12                   | 12-60                     | 22                                   | 22                   | 100                      | 9.09                     | NA                                  |

|                     | 24                   | 24-60                     | 22                                   | 47                   | 100                      | 4.32                     | NA                                  |

#### NOTE:

- 1) The maximum input voltage is limited by the minimum turn-on time  $T_{\text{ON\_MIN}}. \\$

- 2) The inductance value is calculated based on the typical  $V_{\text{IN}}$ =24V.

- 3) All C<sub>OUT</sub> capacitors are values after derating. More capacitors need to be added when ceramic capacitors are used.

- 4) At high frequencies and limited by temperature protection, full load current may not be available at higher voltages.

- 5) For  $R_{FBT}$  not  $1M\Omega$  design, adjust  $C_{ff}$  so that  $C_{ff}$  X  $R_{FBT}$  unchanged, and adjust  $R_{FBT}/R_{FBB}$  unchanged.

- 6) In the case of large ESR output capacitance, there is sufficient phase margin and Cff is not required.

SE8406 Nebula Semiconductor Technology Co., LTD

## **Device selection and calculations**

### **Output voltage setting**

The output voltage VOUT is determined by the divider resistance between VOUT and PGND of FB pin. The resistance value can be selected according to the following formula:

$$R_{FBB} = (\frac{V_{FB}}{V_{OUT} - V_{FB}}) \times R_{FBT}$$

$V_{FB}$  is the internal reference voltage. The upper part resistance R<sub>FBT</sub> generally chooses resistance not greater than 1M $\Omega$ , too large resistance value will weaken the anti-interference ability of the feedback circuit, too small resistance value will increase the static current, reduce the light load efficiency.

#### Set the switching frequency resistance

Switching frequency Fs is determined by external resistance  $R_T$  between FREQ pin and AGND.  $R_T$  resistance can be calculated according to the following formula. 1% precision resistance is recommended.

$$R_T(k\Omega) = \frac{81053}{Fs(kHz)} - 21$$

### Input capacitance selection

In typical applications, a 4.7uF to 10uF X7R or X5R ceramic capacitor with an adequate voltage rating is recommended. To compensate for the derating caused by dc bias of the ceramic capacitor, it is recommended that the rated voltage be twice the maximum input voltage. It is also recommended to use a small package capacitor as close to VIN and PGND pins as possible to absorb high frequency switching noise, such as 0603 package, 0.1uF ceramic capacitor.

#### Inductance selection

The selection of inductance needs to consider the following aspects:

(1) Select inductor to provide the desired current ripple. It is recommended that the current ripple be about 20%-40% of the current maximum output current, and the inductance calculation formula is as follows:

$$L = \frac{V_{OUT} \times (1 - V_{OUT}/V_{IN,MAX})}{f_{SW} \times I_{OUT(MAX)} \times K}$$

$f_{SW}$  is the switching frequency,  $I_{OUT(MAX)}$  is the LED current, and constant K is the percentage of inductance current ripple.

For SE8406, the optimal inductance range for most typical applications is 2.2μH to 15μH.

(2) To ensure circuit safety, the saturation current rating of the inductor must be greater than the peak current at full load. It is recommended that the saturation current of the inductor exceed the peak current at normal operation by 30%-40%. The peak current of inductance can be calculated according to the following formula:

$$I_{L(PEAK)} = I_{OUT(MAX)} + \frac{V_{OUT} \times (1 - V_{OUT}/V_{IN,MAX})}{2 \times f_{SW} \times L}$$

### Output capacitance selection

SE8406 allows a wide range of output capacitors. To ensure cost and small volume, select an appropriate output capacitor. In practical applications, output capacitance will directly affect voltage overshoot/undershoot and output voltage ripple in transient response to output current. When the load transient changes, the output capacitor needs to supply the charge before the loop adjustment is completed, and the transient voltage change value  $\Delta I_{OUT}$  can be calculated by the following formula:

$$\Delta V_{OUT} = \Delta I_{OUT} \times ESR$$

$\Delta I_{OUT}$  represents the jump value of load current, and ESR represents the equivalent series resistance value of output capacitance.

SE8406 13 / 16

Nebula Semiconductor Technology Co., LTD www.nblsemi.com

The output voltage ripple is mainly composed of two parts: one is caused by the inductance current ripple flowing through the ESR of the output capacitor, the other is caused by the inductance current ripple charging and discharging of the output capacitor.

$$\Delta V_{OUT-ripple} = \frac{\Delta I_L}{8 \times C_{OUT} \times F_{SW}} + \Delta I_L \times ESR$$

$\Delta I_L$  represents inductance ripple current,  $F_{SW}$  represents MOSFET switching frequency.

In order to maintain small output voltage overshoot or undershoot and reduce output ripple during transient changes, capacitors with large capacitance and small ESR are required, which also increases cost and volume. It is critical to select the appropriate output capacitance.

### C<sub>vcc</sub> capacitance

The VCC pin is the output of SE8406's internal LDO, which is used to power SE8406's internal control circuit and drive the two internally integrated MOSFETs. The input to this LDO comes from VIN or VCCIN (see internal function block diagram for details). To ensure voltage stability, it is recommended that a 1uF-4.7uF ceramic capacitor be placed as close to VCC and PGND pins as possible, and the rated voltage is recommended to be above 10V.

### **C<sub>VCCIN</sub>** capacitance

This pin is an input to the internal LDO. When the VCCIN pin is not connected, the input to the LDO is connected internally to VIN. Due to the nature of LDO, the pressure difference between input and output can affect LDO efficiency. For applications with output voltages above 5V, the VCCIN pin can be connected to the output voltage for higher light-load efficiency. For this method, it is recommended to place a 1uF ceramic capacitor close to the VCCIN and PGND as the input capacitor for the internal LDO.

## **C**<sub>BST</sub> capacitance

C<sub>BST</sub> capacitor is a bootstrap capacitor in SE8406 application, used to drive high side power tube. In order to ensure voltage stability, it is recommended to place a 0.1uF-1uF ceramic capacitor close to the BST and SW pins with rated voltage above 16V.

### C<sub>SS</sub> Soft starting capacitance

With the SS pin dangling, SE8406 will adopt internal soft start time. To obtain a longer soft start time,  $C_{SS}$  capacitor can be connected to SS pin, and its capacitance value can be obtained from the following formula:

$$C_{ss} = \frac{t_{ss} \times I_{SS\_CHARGE}}{V_{REF}}$$

$I_{SS\_CHARGE}$  is the soft start charging current,  $V_{REF}$  is the internal reference voltage, and  $t_{ss}$  is the target soft start time, whose value should not be less than the internal soft start time.

### Undervoltage lock (UVLO) setting

SE8406 can adjust input undervoltage lock (UVLO) using the external partial voltage resistor network consisting of  $R_{ENH}$  and  $R_{ENL}$ .  $R_{ENH}$  is connected between VIN pin and EN pin.  $R_{ENL}$  is connected between the EN pin and the GND pin. The UVLO value will be determined by the following formula:

$$V_{IN_{RISING}} = \left(1 + \frac{R_{ENH}}{R_{ENL}}\right) \times V_{EN_{UV_R}}$$

$V_{EN\_UV\_R}$  indicates the threshold for the EN function. Note that the set  $V_{IN\_RISING}$  must be higher than the built-in under-voltage lock value 4V on the VIN pin.

### R<sub>PG</sub> setting

The PG pin needs to be pulled up to the VCC or an external voltage source through an external resistor. The recommended pull-up resistance value of the pin ranges from  $10k\Omega$  to  $100k\Omega$ . It should be noted that the pull-up power supply of PG pin should not exceed 6V. Therefore, if the pull-up power supply exceeds the limit, it is recommended to apply a resistance partial voltage between PG pin and PGND.

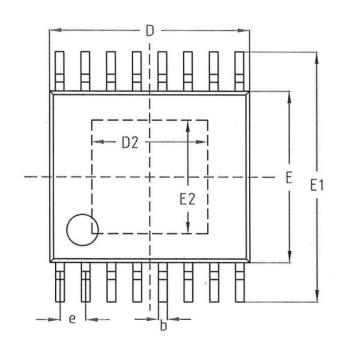

# **Package Information**

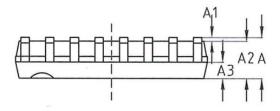

## ETSSOP-16L

| 机械尺寸/mm      |            |                |            |  |  |  |  |

|--------------|------------|----------------|------------|--|--|--|--|

| Dimensions   |            |                |            |  |  |  |  |

| 字符<br>SYMBOL | 最小值<br>MIN | 典型值<br>NOMINAL | 最大值<br>MAX |  |  |  |  |

| Α            | 1          | -              | 1.20       |  |  |  |  |

| A1           | 0.05       | -              | 0.15       |  |  |  |  |

| A2           | 0.90       | 1.00           | 1.05       |  |  |  |  |

| А3           | 0.39       | 0.39 0.44 0.49 |            |  |  |  |  |

| b            | 0.20       | -              | 0.28       |  |  |  |  |

| С            | 0.13       | -              | 0.17       |  |  |  |  |

| D            | 4.90       | 5.00           | 5.10       |  |  |  |  |

| Ε            | 4.30       | 4.40           | 4.50       |  |  |  |  |

| E1           | 6.20       | 6.20 6.40 6.60 |            |  |  |  |  |

| е            |            | 0.65 BSC       | ;          |  |  |  |  |

| L1           | 1.00REF    |                |            |  |  |  |  |

| L            | 0.45       | 0.45 0.60 0.75 |            |  |  |  |  |

| θ            | 0°         | 0 8.           |            |  |  |  |  |

| Size(mm)  LF size(mil) | D2      | E2       |

|------------------------|---------|----------|

| 118*91                 | 2.80REF | 2. 10REF |

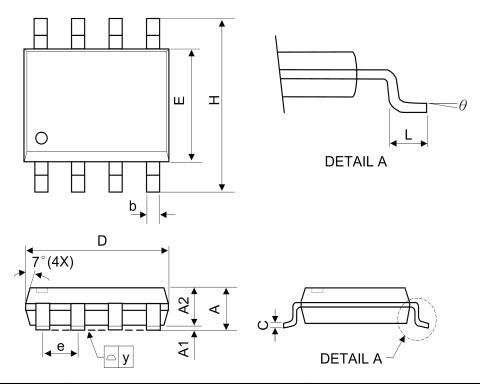

## ESOP-8

| Crumb ol |          | Millimetre |      | Inch   |           |       |  |

|----------|----------|------------|------|--------|-----------|-------|--|

| Symbol   | Min      | Тур        | Max  | Min    | Тур       | Max   |  |

| A        | -        | -          | 1.75 | -      | -         | 0.069 |  |

| A1       | 0.1      | -          | 0.25 | 0.04   | -         | 0.1   |  |

| A2       | 1.25     | -          | -    | 0.049  | -         | -     |  |

| С        | 0.1      | 0.2        | 0.25 | 0.0075 | 0.008     | 0.01  |  |

| D        | 4.7      | 4.9        | 5.1  | 0.185  | 0.193     | 0.2   |  |

| Е        | 3.7      | 3.9        | 4.1  | 0.146  | 0.154     | 0.161 |  |

| Н        | 5.8      | 6          | 6.2  | 0.228  | 0.236     | 0.244 |  |

| L        | 0.4      | 1          | 1.27 | 0.015  | -         | 0.05  |  |

| b        | 0.31     | 0.41       | 0.51 | 0.012  | 0.016     | 0.02  |  |

| e        | 1.27 BSC |            |      |        | 0.050 BSC |       |  |

| у        | -        | 1          | 0.1  | -      | -         | 0.004 |  |

| θ        | 0°       | -          | 8°   | 0°     | -         | 8°    |  |